12.20_Digital logic

一、编码

- 格雷码的作用:当电子器件的变化速度不一致时,便会产生错误代码,尽管这种错误代码出现的时间是短暂的,但有时是不允许的,因为它将形成干扰,影响数字系统的正常工作。格雷码从编 码上杜绝了这类错误的发生。

- 奇偶检验码的作用: 在发送端由编码器根据信息位编码产生奇偶检验位,形成奇偶检验码发往接收端;接收端通过检测器检查代码中含“1”个数的奇偶,判断信息是否出错。

8421码:10.11.12.13.14.15

2421码:5.6.7.8.9.10

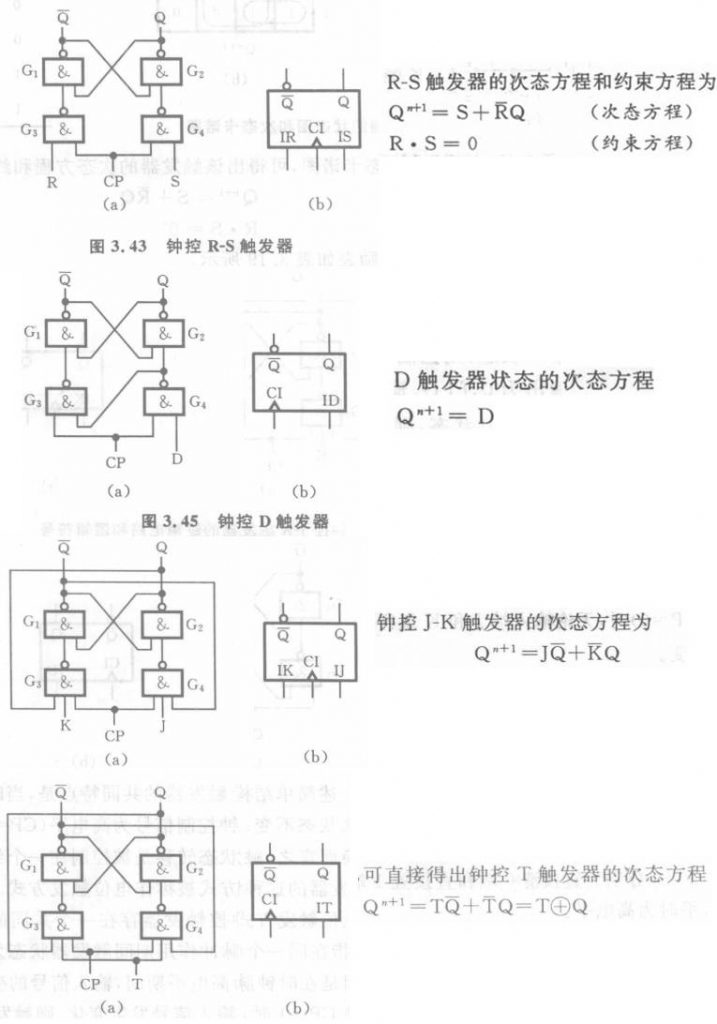

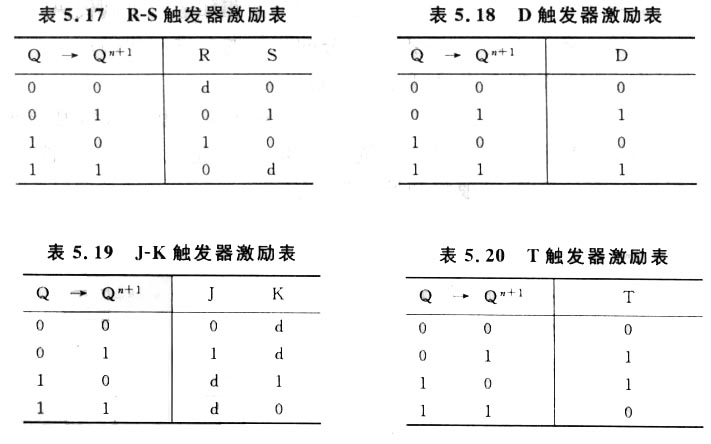

二、触发器

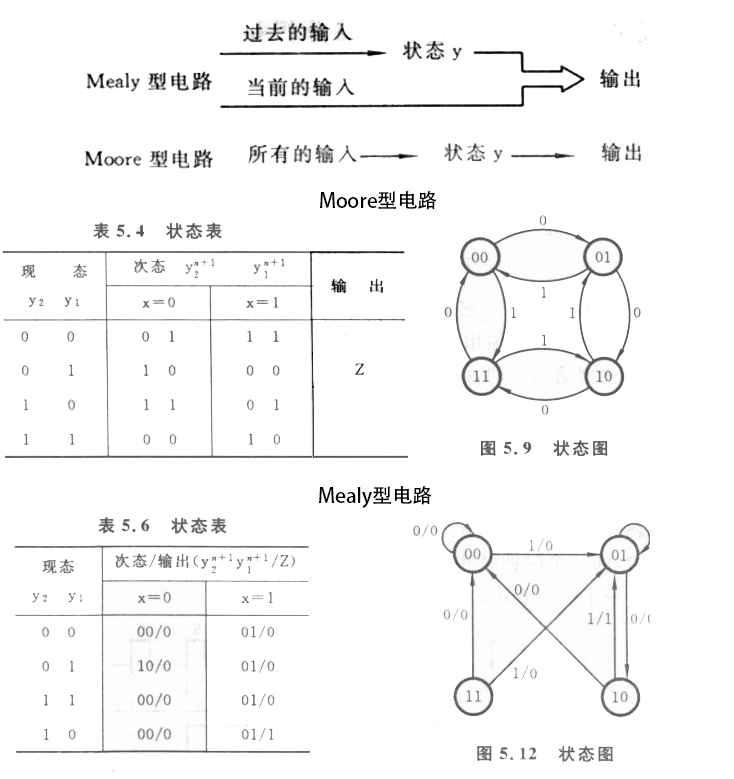

三、Moore和Merly型电路

四、电路的分析与设计

1、组合逻辑电路分析

- 根据电路图写出逻辑表达式

- 化简输出函数表达式

- 写出输出函数真值表

- 功能评述

2、组合逻辑电路的设计

- 分析问题,写真值表,写出函数的最小项表达式

- 求函数最简表达式

- 选择逻辑门类型并实现逻辑函数的变换

- 画出电路图

3、同步时序电路分析

- 写出输出函数和激励函数表达式

- 列出电路次态真值表(输入x,现态y,激励函数(根据触发器类型RS,D,JK,T),次态yn+1)

- 做出状态图和状态表

- 电路的状态响应序列和输出序列、时间图和文字描述电路

4、同步时序电路设计

- 形成原始状态图和原始状态表

- 状态化简(隐含表化简)

- 状态编码

- 确定激励函数和输出函数并画出逻辑电路图

五、中规模组合逻辑电路、

4位并行加法器:74283

二进制3-8译码器:74138

二-十进制译码器:7442

七段显示译码器:7448

优先编码器:74148

4选1多路选择器(MUX):74153

8选1多路选择器(MUX):74152

全加器的设计

4位加法器设计

n位加法器设计

8421BCD码加法器设计

4选1多路选择器设计

3-8译码器设计

4-2优先编码器设计

4位无符号比较器设计

数码驱动器设计

74-381ALU设计

No responses yet